LAN91C110 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LAN91C110 Datasheet PDF : 56 Pages

| |||

FEAST Fast Ethernet Controller for PCMCIA and Generic 16-Bit Applications

Datasheet

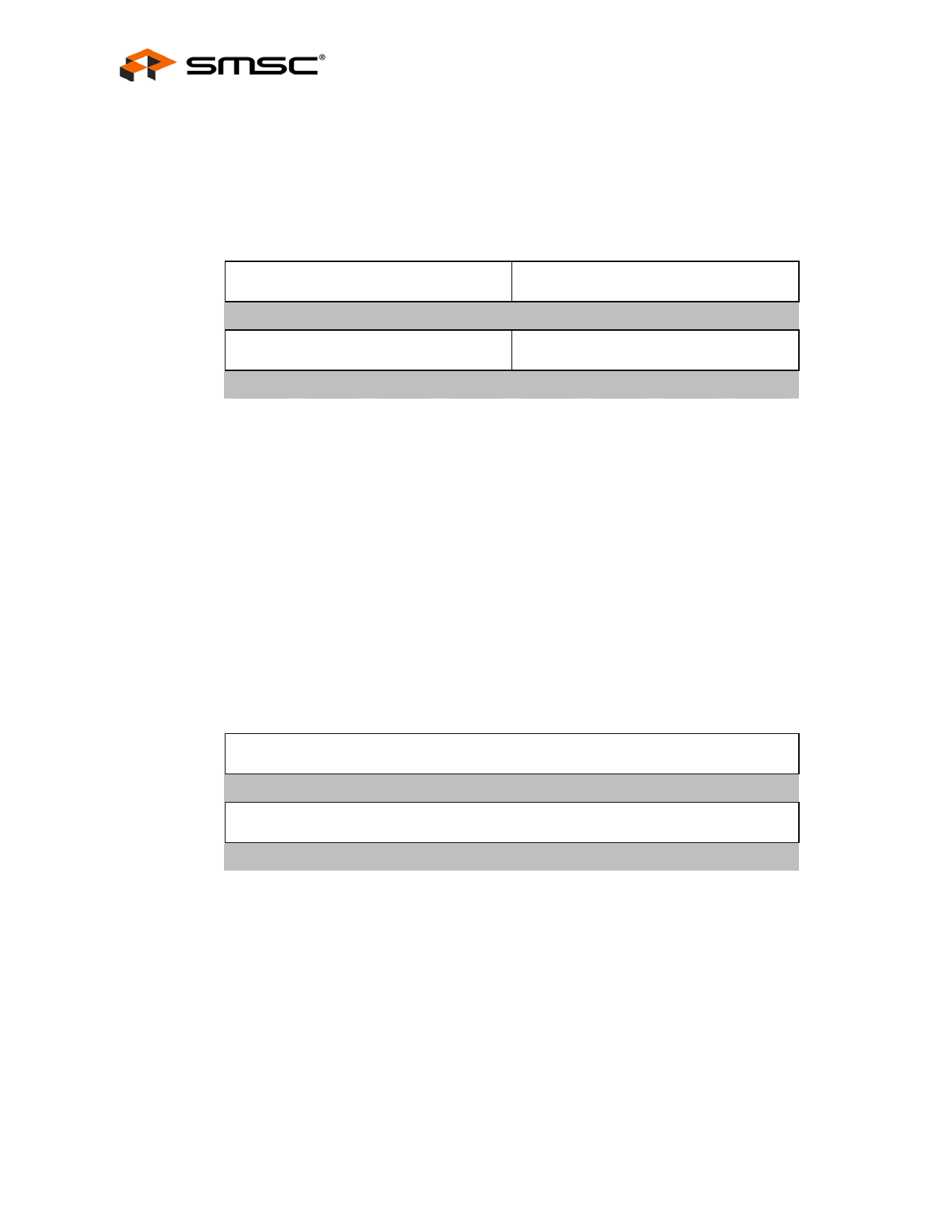

BANK 0

OFFSET

6

NAME

COUNTER REGISTER

TYPE

READ ONLY

SYMBOL

ECR

Counts four parameters for MAC statistics. When any counter reaches 15 an interrupt is issued. All counters are cleared

when reading the register and do not wrap around beyond 15.

HIGH

BYTE

LOW

BYTE

NUMBER OF EXC. DEFFERED TX

0

0

0

0

MULTIPLE COLLISION COUNT

0

0

0

0

NUMBER OF DEFFERED TX

0

0

0

0

SINGLE COLLISION COUNT

0

0

0

0

Each four bit counter is incremented every time the corresponding event, as defined in the EPH STATUS REGISTER bit

description, occurs. Note that the counters can only increment once per enqueued transmit packet, never faster, limiting

the rate of interrupts that can be generated by the counters. For example if a packet is successfully transmitted after one

collision the SINGLE COLLISION COUNT field is incremented by one. If a packet experiences between 2 to 16 collisions,

the MULTIPLE COLLISION COUNT field is incremented by one. If a packet experiences deferral the NUMBER OF

DEFERRED TX field is incremented by one, even if the packet experienced multiple deferrals during its collision retries.

The COUNTER REGISTER facilitates maintaining statistics in the AUTO RELEASE mode where no transmit interrupts

are generated on successful transmissions.

Reading the register in the transmit service routine will be enough to maintain statistics.

BANK 0

OFFSET

8

NAME

MEMORY INFORMATION REGISTER

TYPE

READ ONLY

SYMBOL

MIR

HIGH

BYTE

FREE MEMORY AVAILABLE (IN BYTES * 256 * M)

1

1

1

1

1

1

1

1

LOW

BYTE

MEMORY SIZE (IN BYTES *256 * M)

1

1

1

1

1

1

1

1

FREE MEMORY AVAILABLE - This register can be read at any time to determine the amount of free memory. The

register defaults to the MEMORY SIZE upon reset or upon the RESET MMU command.

MEMORY SIZE - This register can be read to determine the total memory size.

All memory related information is represented in 256 * M byte units, where the multiplier M is determined by the MCR

upper byte.

These register default to FFh, which should be interpreted as 256.

SMSC LAN91C110 Rev. B

Page 22

DATASHEET

Revision 1.0 (11-04-08)