LAN91C110 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LAN91C110 Datasheet PDF : 56 Pages

| |||

FEAST Fast Ethernet Controller for PCMCIA and Generic 16-Bit Applications

Datasheet

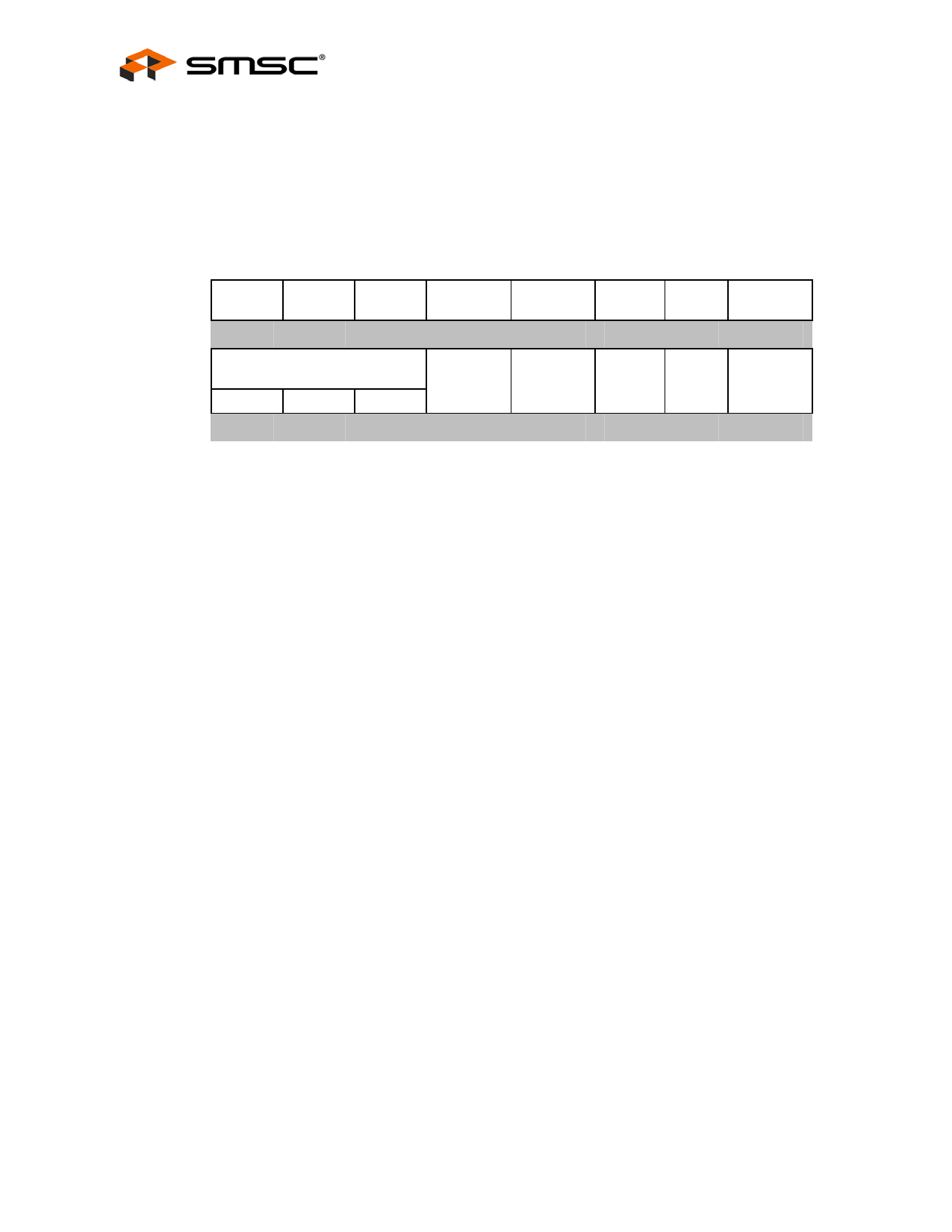

BANK2

OFFSET

0

NAME

MMU COMMAND REGISTER

TYPE

WRITE ONLY

BUSY Bit Readable

SYMBOL

MMUCR

This register is used by the CPU to control the memory allocation, de-allocation, TX FIFO and RX FIFO control. The three

command bits determine the command issued as described below:

HIGH

BYTE

LOW

BYTE

COMMAND

X

Y

Z

Reserved Reserved

N2

N1 N0/BUSY

0

COMMAND SET:

xyz

000 0) NOOP - NO OPERATION

001 1)

ALLOCATE MEMORY FOR TX - N2, N1, N0 defines the amount of memory requested as (value + 1) * 256

bytes. Namely N2, N1, N0 = 1 will request 2 * 256 = 512 bytes. A shift-based divide by 256 of the packet

length yields the appropriate value to be used as N2, N1, N0. Immediately generates a completion code at

the ALLOCATION RESULT REGISTER. Can optionally generate an interrupt on successful completion. N2,

N1, N0 are ignored by the LAN91C110 but should be implemented in LAN91C110 software drivers for

LAN9000 compatibility.

010 2) RESET MMU TO INITIAL STATE - Frees all memory allocations, clears relevant interrupts, resets packet

FIFO pointers.

011 3)

REMOVE FRAME FROM TOP OF RX FIFO - To be issued after CPU has completed processing of present

receive frame. This command removes the receive packet number from the RX FIFO and brings the next

receive frame (if any) to the RX area (output of RX FIFO).

100 4)

REMOVE AND RELEASE TOP OF RX FIFO - Like 3) but also releases all memory used by the packet

presently at the RX FIFO output. The MMU busy time after issuing REMOVE and RELEASE command

depends on the time when the busy bit is cleared. The time from issuing REMOVE and RELEASE command

on the last receive packet to the time when receive FIFO is empty depends on RX INT bit turning low. An

alternate approach can be checking the read RX FIFO register.

101 5)

RELEASE SPECIFIC PACKET - Frees all pages allocated to the packet specified in the PACKET NUMBER

REGISTER. Should not be used for frames pending transmission. Typically used to remove transmitted

frames, after reading their completion status. Can be used following 3) to release receive packet memory in

a more flexible way than 4).

110 6) ENQUEUE PACKET NUMBER INTO TX FIFO - This is the normal method of transmitting a packet just

loaded into RAM. The packet number to be enqueued is taken from the PACKET NUMBER REGISTER.

111 7) RESET TX FIFOs - This command will reset both TX FIFOs: The TX FIFO holding the packet numbers

awaiting transmission and the TX Completion FIFO. This command provides a mechanism for canceling

packet transmissions, and reordering or bypassing the transmit queue. The RESET TX FIFOs command

should only be used when the transmitter is disabled. Unlike the RESET MMU command, the RESET TX

FIFOs does not release any memory.

SMSC LAN91C110 Rev. B

Page 27

DATASHEET

Revision 1.0 (11-04-08)