RTL8139D Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8139D Datasheet PDF : 67 Pages

| |||

RTL8139DL

Datasheet

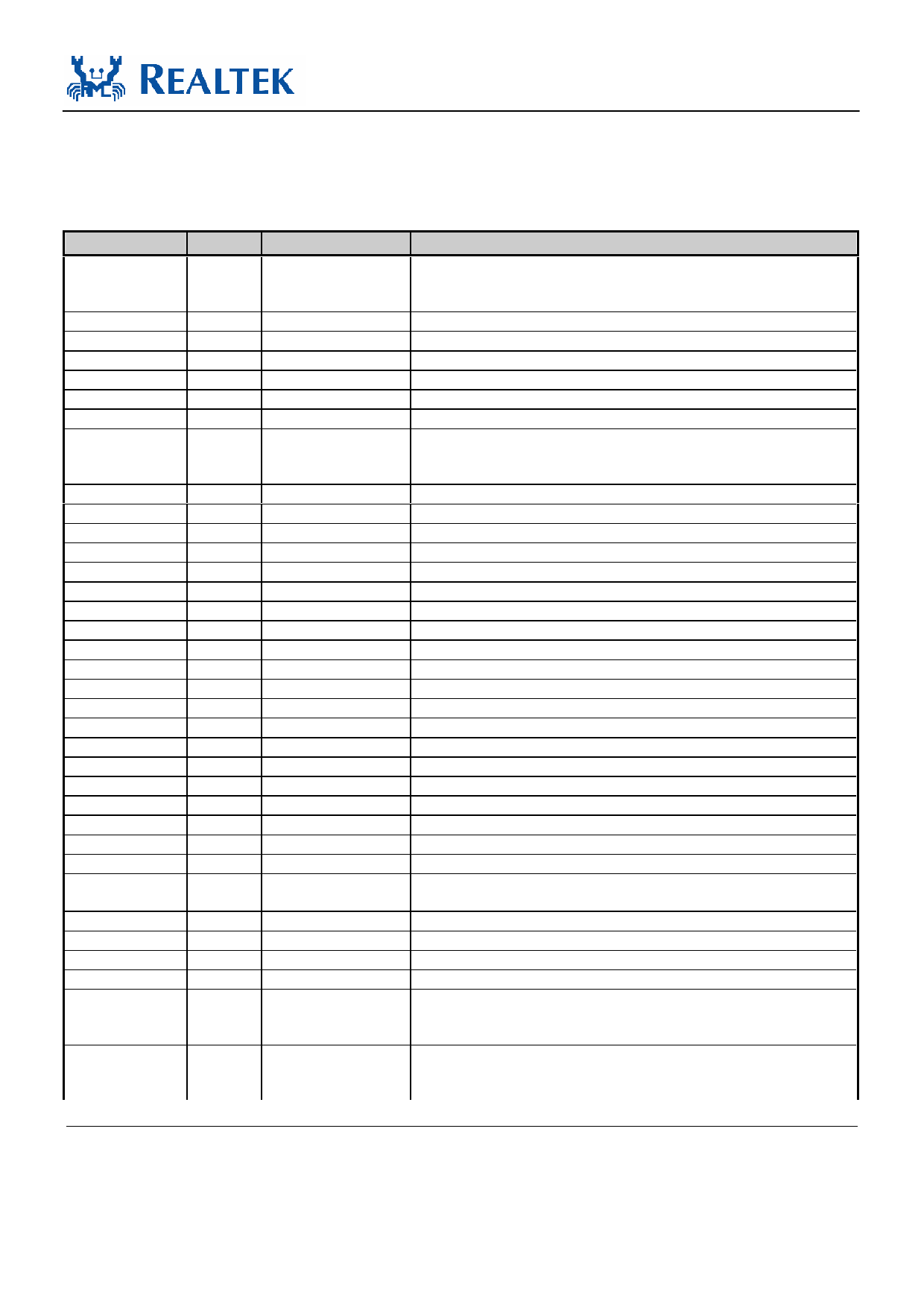

5. Register Descriptions

The RTL8139D(L) provides the following set of operational registers mapped into PCI memory space or

I/O space.

Offset

0000h

R/W Tag

R/W

IDR0

0001h

R/W

0002h

R/W

0003h

R/W

0004h

R/W

0005h

R/W

0006h-0007h

-

0008h

R/W

IDR1

IDR2

IDR3

IDR4

IDR5

-

MAR0

0009h

R/W

000Ah

R/W

000Bh

R/W

000Ch

R/W

000Dh

R/W

000Eh

R/W

000Fh

R/W

0010h-0013h

R/W

0014h-0017h

R/W

0018h-001Bh

R/W

001Ch-001Fh

R/W

0020h-0023h

R/W

0024h-0027h

R/W

0028h-002Bh

R/W

002Ch-002Fh

R/W

0030h-0033h

R/W

0034h-0035h

R

0036h

R

0037h

R/W

0038h-0039h

R/W

003Ah-003Bh

R

003Ch-003Dh R/W

003Eh-003Fh

R/W

0040h-0043h

R/W

0044h-0047h

R/W

0048h-004Bh

R/W

MAR1

MAR2

MAR3

MAR4

MAR5

MAR6

MAR7

TSD0

TSD1

TSD2

TSD3

TSAD0

TSAD1

TSAD2

TSAD3

RBSTART

ERBCR

ERSR

CR

CAPR

CBR

IMR

ISR

TCR

RCR

TCTR

004Ch-004Fh

R/W

MPC

Description

ID Register 0, The ID register0-5 are only permitted to read/write by

4-byte access. Read access can be byte, word, or double word access.

The initial value is autoloaded from EEPROM EthernetID field.

ID Register 1

ID Register 2

ID Register 3

ID Register 4

ID Register 5

Reserved

Multicast Register 0, The MAR register0-7 are only permitted to

read/write by 4-byte access. Read access can be byte, word, or double

word access. Driver is responsible for initializing these registers.

Multicast Register 1

Multicast Register 2

Multicast Register 3

Multicast Register 4

Multicast Register 5

Multicast Register 6

Multicast Register 7

Transmit Status of Descriptor 0

Transmit Status of Descriptor 1

Transmit Status of Descriptor 2

Transmit Status of Descriptor 3

Transmit Start Address of Descriptor0

Transmit Start Address of Descriptor1

Transmit Start Address of Descriptor2

Transmit Start Address of Descriptor3

Receive (Rx) Buffer Start Address

Early Receive (Rx) Byte Count Register

Early Rx Status Register

Command Register

Current Address of Packet Read

Current Buffer Address: The initial value is 0000h. It reflects total

received byte-count in the rx buffer.

Interrupt Mask Register

Interrupt Status Register

Transmit (Tx) Configuration Register

Receive (Rx) Configuration Register

Timer CounT Register: This register contains a 32-bit general-purpose

timer. Writing any value to this 32-bit register will reset the original

timer and begin to count from zero.

Missed Packet Counter: Indicates the number of packets discarded due

to Rx FIFO overflow. It is a 24-bit counter. After s/w reset, MPC is

cleared. Only the lower 3 bytes are valid.

Single Chip Multifunction 10/100 Ethernet Controller w/Power Management 8 Track ID: JATR-1076-21 Rev. 1.2