RTL8139D Ver la hoja de datos (PDF) - Unspecified

Número de pieza

componentes Descripción

Lista de partido

RTL8139D Datasheet PDF : 67 Pages

| |||

RTL8139DL

Datasheet

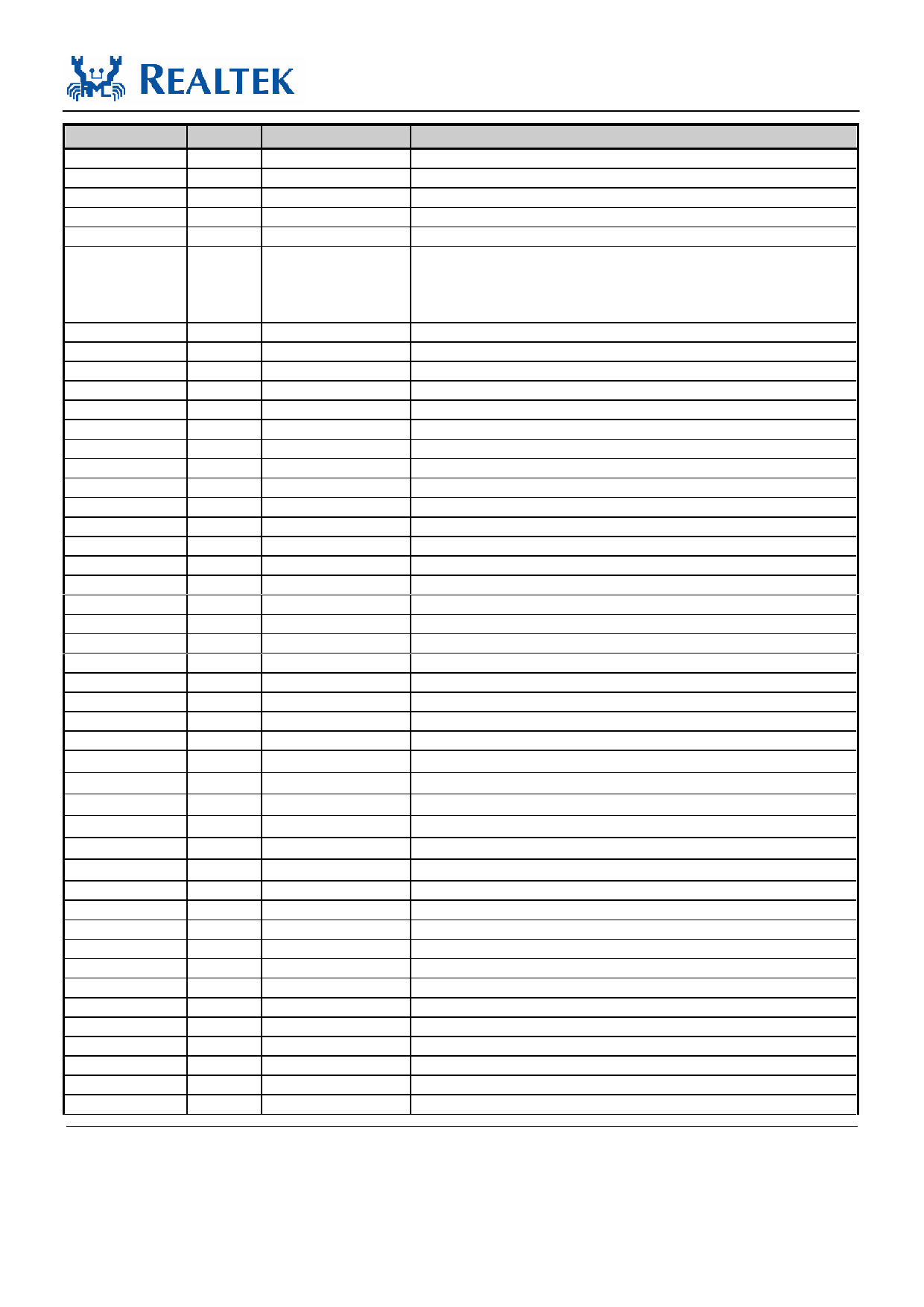

Offset

R/W Tag

0050h

0051h

0052h

0053H

0054h-0057h

R/W

R/W

R/W

-

R /W

9346CR

CONFIG0

CONFIG1

-

TimerInt

0058h

R/W

0059h

R/W

005Ah

R/W

005Bh

-

005Ch-005Dh R/W

005Eh

R

005Fh

-

0060h-0061h

R

0062h-0063h

R/W

0064h-0065h

R

0066h-0067h

R/W

0068h-0069h

R

006Ah-006Bh

R

006Ch-006Dh

R

006Eh-006Fh

R

0070h-0071h

R/W

0072h-0073h

R

0074h-0075h

R/W

0076-0077h

-

0078h-007Bh

R/W

007Ch-007Fh

R/W

0080h

R/W

0081-0083h

-

0084h

R/W

0085h

R/W

0086h

R/W

0087h

R/W

0088h

R/W

0089h

R/W

008Ah

R/W

008Bh

R/W

008Ch–0093h R/W

0094h–009Bh R/W

009Ch–00A3h R/W

00A4h–00ABh R/W

00ACh–00B3h R/W

00B4h–00BBh R/W

00BCh–00C3h R/W

00C4h–00CBh R/W

00CCh

R/W

MSR

CONFIG3

CONFIG4

-

MULINT

RERID

-

TSAD

BMCR

BMSR

ANAR

ANLPAR

ANER

DIS

FCSC

NWAYTR

REC

CSCR

-

PHY1_PARM

TW_PARM

PHY2_PARM

-

CRC0

CRC1

CRC2

CRC3

CRC4

CRC5

CRC6

CRC7

Wakeup0

Wakeup1

Wakeup2

Wakeup3

Wakeup4

Wakeup5

Wakeup6

Wakeup7

LSBCRC0

Description

When written any value, MPC will be reset also.

93C46 Command Register

Configuration Register 0

Configuration Register 1

Reserved

Timer Interrupt Register. Once having written a nonzero value to this

register, the Timeout bit of ISR register will be set whenever the

TCTR reaches to this value. The Timeout bit will never be set as long

as TimerInt register is zero.

Media Status Register

Configuration register 3

Configuration register 4

Reserved

Multiple Interrupt Select

PCI Revision ID = 10h.

Reserved.

Transmit Status of All Descriptors

Basic Mode Control Register

Basic Mode Status Register

Auto-Negotiation Advertisement Register

Auto-Negotiation Link Partner Register

Auto-Negotiation Expansion Register

Disconnect Counter

False Carrier Sense Counter

N-way Test Register

RX_ER Counter

CS Configuration Register

Reserved.

PHY parameter 1

Twister parameter

PHY parameter 2

Reserved

Power Management CRC register0 for wakeup frame0

Power Management CRC register1 for wakeup frame1

Power Management CRC register2 for wakeup frame2

Power Management CRC register3 for wakeup frame3

Power Management CRC register4 for wakeup frame4

Power Management CRC register5 for wakeup frame5

Power Management CRC register6 for wakeup frame6

Power Management CRC register7 for wakeup frame7

Power Management wakeup frame0 (64bit)

Power Management wakeup frame1 (64bit)

Power Management wakeup frame2 (64bit)

Power Management wakeup frame3 (64bit)

Power Management wakeup frame4 (64bit)

Power Management wakeup frame5 (64bit)

Power Management wakeup frame6 (64bit)

Power Management wakeup frame7 (64bit)

LSB of the mask byte of wakeup frame0 within offset 12 to 75

Single Chip Multifunction 10/100 Ethernet Controller w/Power Management 9 Track ID: JATR-1076-21 Rev. 1.2