MTD800 Ver la hoja de datos (PDF) - Myson Century Inc

Número de pieza

componentes Descripción

Lista de partido

MTD800 Datasheet PDF : 42 Pages

| |||

MYSON

TECHNOLOGY

MTD 800

(Preliminary)

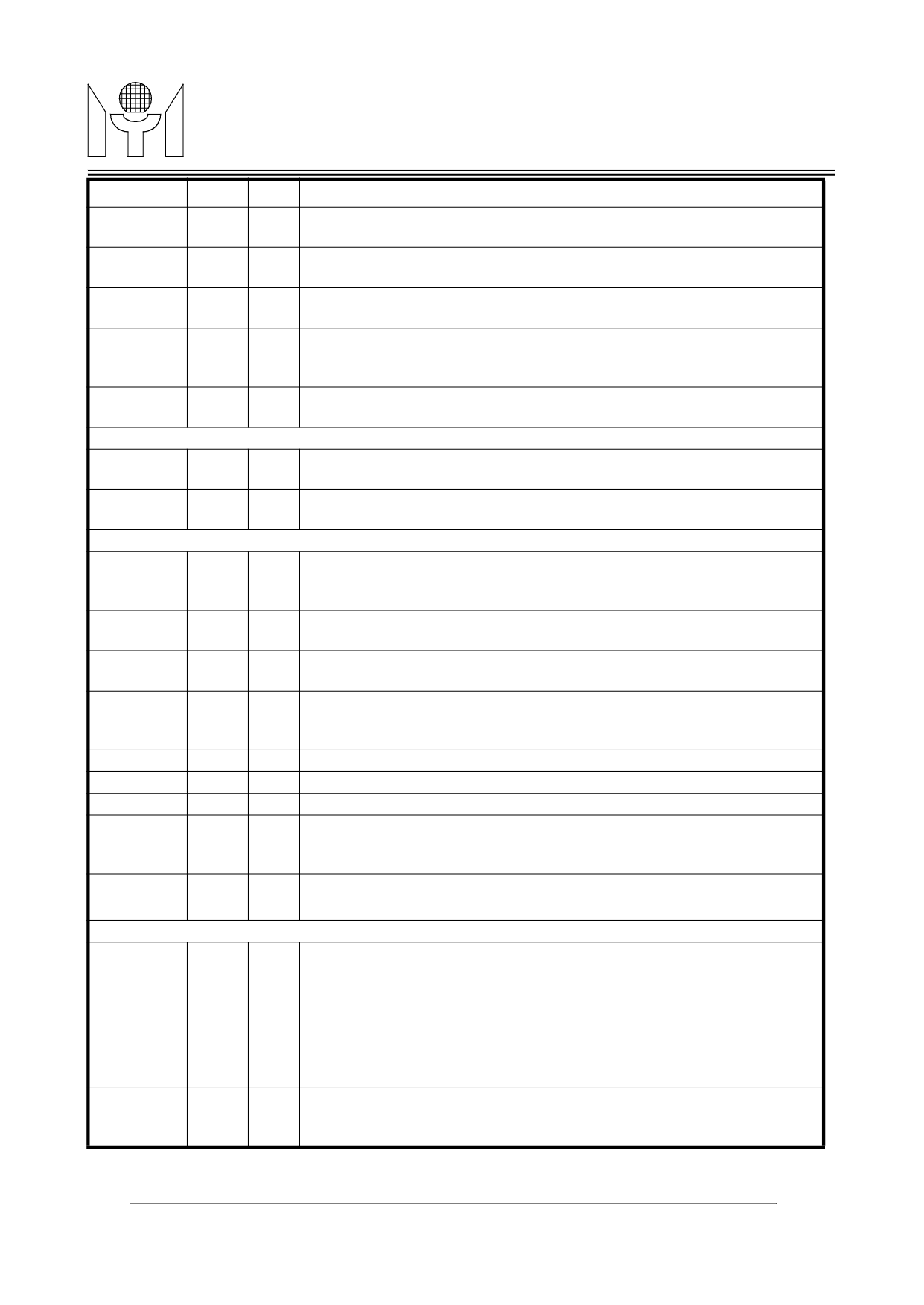

Name

RXD[3:0]

RXER

CRS

Pin #

107 -

110

106

105

MDC

100

MDIO

101

LED_ACT# 98

LED_PAUS

E#

99

ECS

56

BRRD#

57

BRWR#

58

BRCS#

59

BRD0/EEDI 60

BRD1/EEDO 61

BRD2/EECK 62

BRD[7:3]

70 - 69,

66 - 65,

63

BRA[16:0]

89- 80,

77 - 71

WAKEUP/

STSCHG

53

ByPass# 96

I/O

Descriptions

I

Receive Data signals. RXD are driven by PHY and transit synchronously

with respect to the RXCK.

I

Receive Error signal. RXER is asserted high to indicate a coding error is

detected by PHY. This signal is synchronous to RXCK.

I

Carrier Sense signal. CRS is asserted by PHY when either the transmit or

receive medium is non-idle. This signal is asynchronous to TXCK or RXCK.

Management Data Clock. MDC is sourced by the MTD800 to control the

O transfer of the MDIO data. A 1.5K pull up resistor is required to connect to

this pin.

I/O

Management Data Input/Output. A bi-directional data interface connected

to PHY. A 1.5K pull up resistor is required to connect to this pin.

LED Status Output

O

Activity LED. This signal will drive the led light on when detecting activity on

MII interface. A 510 ohm pull up resistor is required to connect to this pin.

O

Pause LED. This signal will drive the led light on when detecting transmis-

sion is paused under the condition of receiving a XON frame.

BootROM/ EEPROM Interface

A chip select signal for the external EEPROM. EEPROM is used to provide

O the configuration data and Ethernet Address. A 100K pull-up resister is con-

nected to this pin.

O

BootROM read signal. Read out the content of BootROM onto the memory

support data bus.

O

BootROM write signal. When flash memory is used, BRWR# is asserted

low to enable the write action.

A chip select signal for the external EPROM (BootROM) or flash memory.

O The BootROM contains codes that can be usually executed for a system

boot function.

I/O A multiplexed signal for BootROM data bit 0 and Serial ROM Data input.

I/O A multiplexed signal for BootROM data bit 1 and Serial ROM Data output.

I/O A multiplexed signal for BootROM data bit 2 and Serial ROM Clock signal.

I/O BootROM data bus from bit 3 to bit 7.

O BootROM address bus from bit 0 to bit 16.

Misc. Interface

Wakeup Pin/CardBus STSCHG Pin.

In PCI application, this pin is the Wakeup pin to signal the host system of an

wakeup event happened.

O/Z In Card bus application, this pin is used as the STSCHG pin to signal the system of

any status changed. This pin is enabled as STSCHG pin if the PME_Enable bit of

the power management control register is set and the FMR.GWAKE, FMR.WAKE

are both set.

EEPROM Bypass Mode. When asserted low, the EEPROM function will be dis-

I able. This is useful for testing purpose. For normal operation, it should be con-

nected to VDD.

4/42

MTD800 Revision 0.0 07/20/1999