MTD800 Ver la hoja de datos (PDF) - Myson Century Inc

Número de pieza

componentes Descripción

Lista de partido

MTD800 Datasheet PDF : 42 Pages

| |||

Bit

31

30

29

28

27

26

25

24 - 22

21 - 11

10 - 0

MYSON

TECHNOLOGY

MTD 800

(Preliminary)

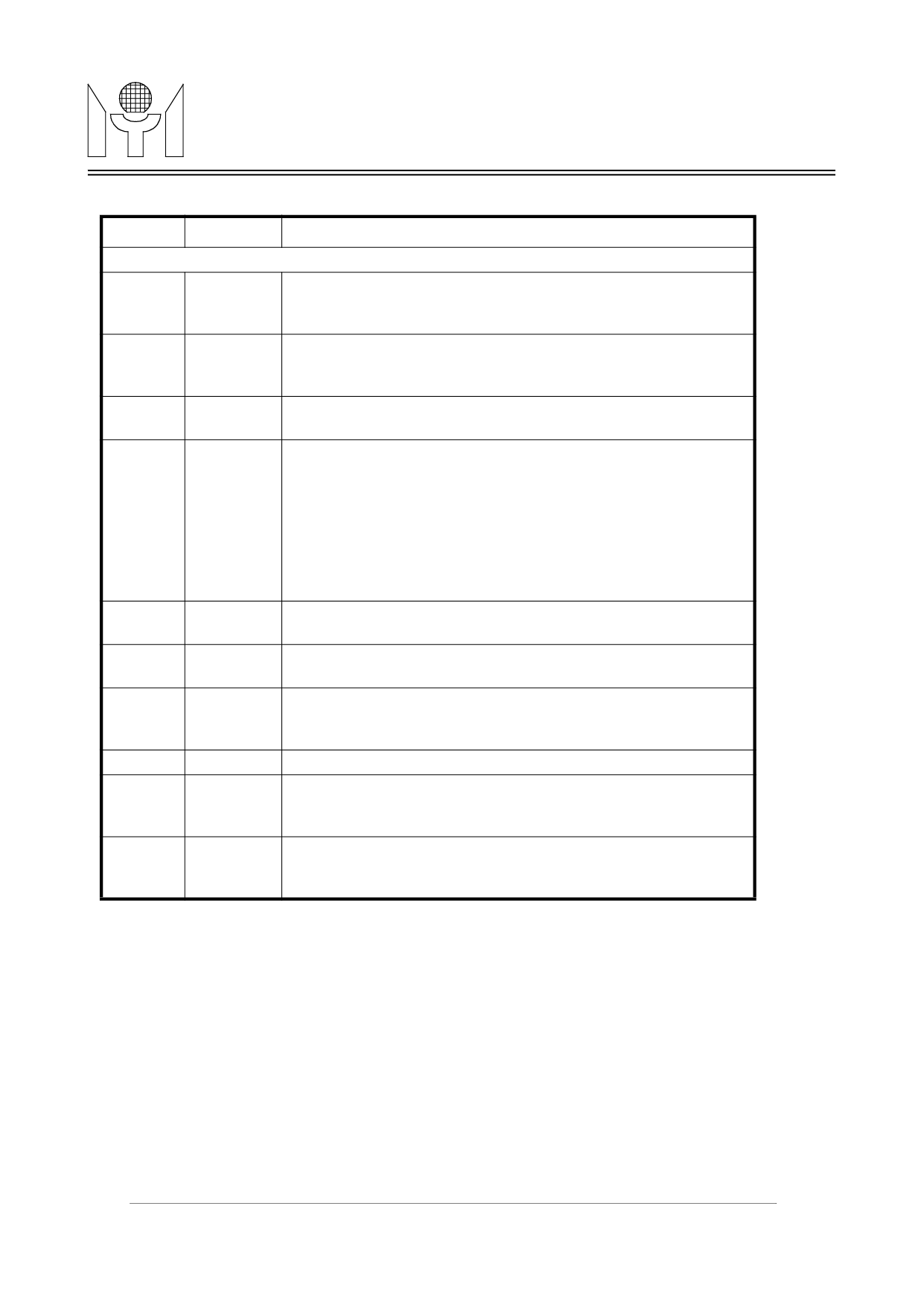

Table 3.2 Transmit Descriptor 1 ( TDES1 )

Symbol

IC

EIC

LD

FD

CRC

PAD

RTLC

-

PKTS[10:0]

TBS

Descr iption

Transmit Configure Word (TCW)

Interrupt Control: This bit supports for interrupt Pacing. When set, indi-

cates that MTD800 will issue interrupt after the packet has been transmit-

ted.

Early Interrupt Control: This bit supports for interrupt Pacing. When set,

indicates that MTD800 will issue interrupt after the packet has been

transferred into the internal FIFO.

Last Descriptor: When set, it means the pointed buffer contains the last

segment of a frame.

First Descriptor: When set, it means the buffer contains the first segment

of a frame. In descriptor ring structure, each buffer is classified as follows

: FD LD Description

1 1 Single buffer descriptor

1 0 First buffer descriptor, further buffer chained

0 1 Chained buffer packet end

0 0 Intermediate buffer.

CRC append : When set, the MTD800 will generate a CRC field to

append to the transmitted packet.

PAD control : When set, the MTD800 will automatically pad zero’s to

the end of packet whose length is less than 64 bytes.

Retry Late Collision : When set, the late collision will be considered as a

normal collision and the MTD800 just increases a collision count instead

of aborting the packet.

Reserved.

Packet Size : This field contains the length of the transmitted packet. The

value should be valid for the first descriptor. The size is indicated in

bytes.

Transmit Buffer Size : This field contains the size information of buffer.

If the transmitted packet only use one single buffer, the TBS should be

equal to PKTS. The size is also indicated in bytes.

3.3 DMA Receive Function

The DMA Receive Function is responsible for collecting the network nibble-stream into the on-chip receive

FIFO, and then transferring the data onto the host’s memory if the fullness of FIFO reaches the predefined

PCI burst length. The data structure for the receive buffer is a forward-link buffer chain which is similar to the

transmit buffer. Descriptors that reside in the host memory act as pointers to these receive buffers. The

descriptor format is shown as figure 3.3. It consists of four long words. The first two words contain the receive

frame status, frame length and the descriptor ownership information. The last two words are the address

pointers for the current data buffer and the next descriptor. The bit field definition of the descriptor words are

given in table 3.3 and table 3.4 respectively. Note that the receive buffers and descriptors address both should

be longword aligned. At the beginning, the driver allocates a set of free buffers and makes the ownership of

these buffers belong to the chip. The MTD800 starts to fetches the first descriptor into its internal registers.

8/42

MTD800 Revision 0.0 07/20/1999