A6850 Ver la hoja de datos (PDF) - Altera Corporation

Número de pieza

componentes Descripción

Lista de partido

A6850 Datasheet PDF : 15 Pages

| |||

a6850 Asynchronous Communications Interface Adapter Data Sheet

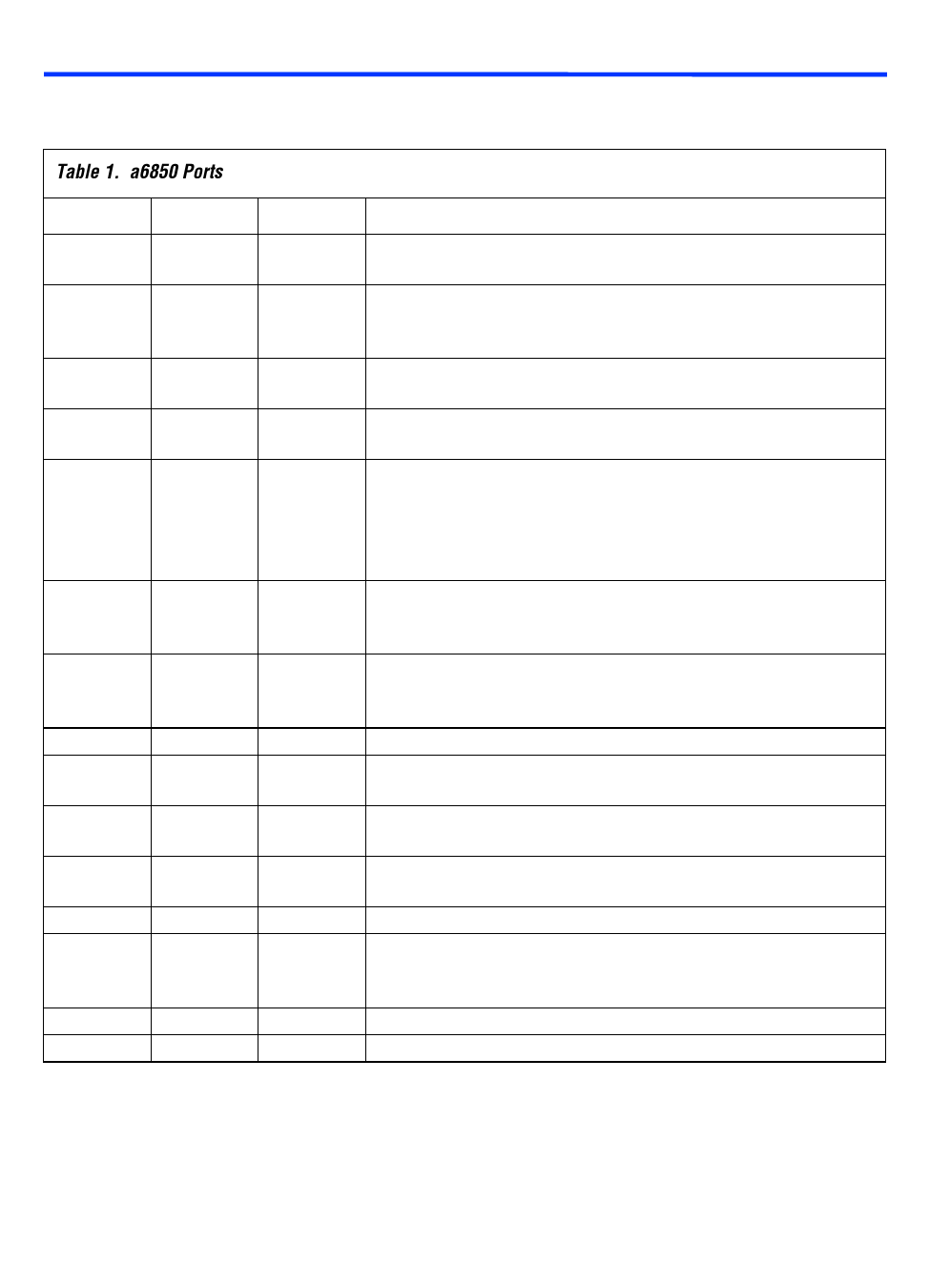

Table 1 describes the input and output ports of the a6850.

Table 1. a6850 Ports

Name

ncts

Type

Input

ndcd

Input

e

nreset

rs

Input

Input

Input

rnw

Input

rxclk

Input

rxdata

txclk

cs[2..0]

di[7..0]

nirq

nrts

Input

Input

Input

Input

Output

Output

txdata

do[7..0]

Output

Output

Polarity

Low

Low

High

Low

–

Low

–

–

–

–

–

Low

Low

–

–

Description

Clear to send, a modem signal name. The ncts input inhibits the

assertion of the transmit data register empty (tdre) status bit.

Data carrier detect, a modem signal name. When the ndcd signal

transitions from low to high, an interrupt to the microprocessor is

generated.

Enable for the microprocessor interface. When e is high, the

microprocessor can access the registers.

Asynchronous reset for the registers and control logic. The nreset

pin was not included in the original MC6850 device.

Register select. This input selects the register based on rnw. If rnw

is high (signaling a read operation), then rs = 1 selects the receiver

data register and rs = 0 selects the status register. However, if rnw

is low (signaling a write operation), then rs = 1 selects the

transmitter data register and rs = 0 selects the control register.

Read/write register controls. When rnw is high, the microprocessor

reads the registers; when rnw is low, the microprocessor writes to

the registers.

Receive clock. The receive control register samples rxdata based

on rxclk and the state of the counter divide select (cds) bits in the

control register.

Receive data. Serial data input from the modem or peripheral.

Transmit clock. Data is asserted to txdata on the falling edge of

txclk.

Chip select from the microprocessor. Chip select must be in the 110

state for the a6850 to be selected.

Parallel data input from the microprocessor or other controlling

device.

Interrupt request to microprocessor.

Request to send. Bits 5 and 6 (transmitter control bits) of the control

register set the nrts bit. The nrts signal is asserted when bit 6 is

low, or bits 5 and 6 are both high.

Transmit data. Serial output to the modem or peripheral.

Parallel data output to the microprocessor or other controlling device.

82

Altera Corporation