A6850 Ver la hoja de datos (PDF) - Altera Corporation

Número de pieza

componentes Descripción

Lista de partido

A6850 Datasheet PDF : 15 Pages

| |||

a6850 Asynchronous Communications Interface Adapter Data Sheet

Transmitter Data Register

The transmitter data register (TDR) is written to by the microprocessor or

other controlling device. Once the existing data bits in the output shift

register are completely transmitted out, the TDR transfers new data into

the output shift register.

Receiver Data Register

The receiver data register (RDR) is written to by the input shift register.

Once the existing data in the RDR is read, the input shift register transfers

new data into the RDR. If 7-bit data is selected, bit 7 is set to a logic low.

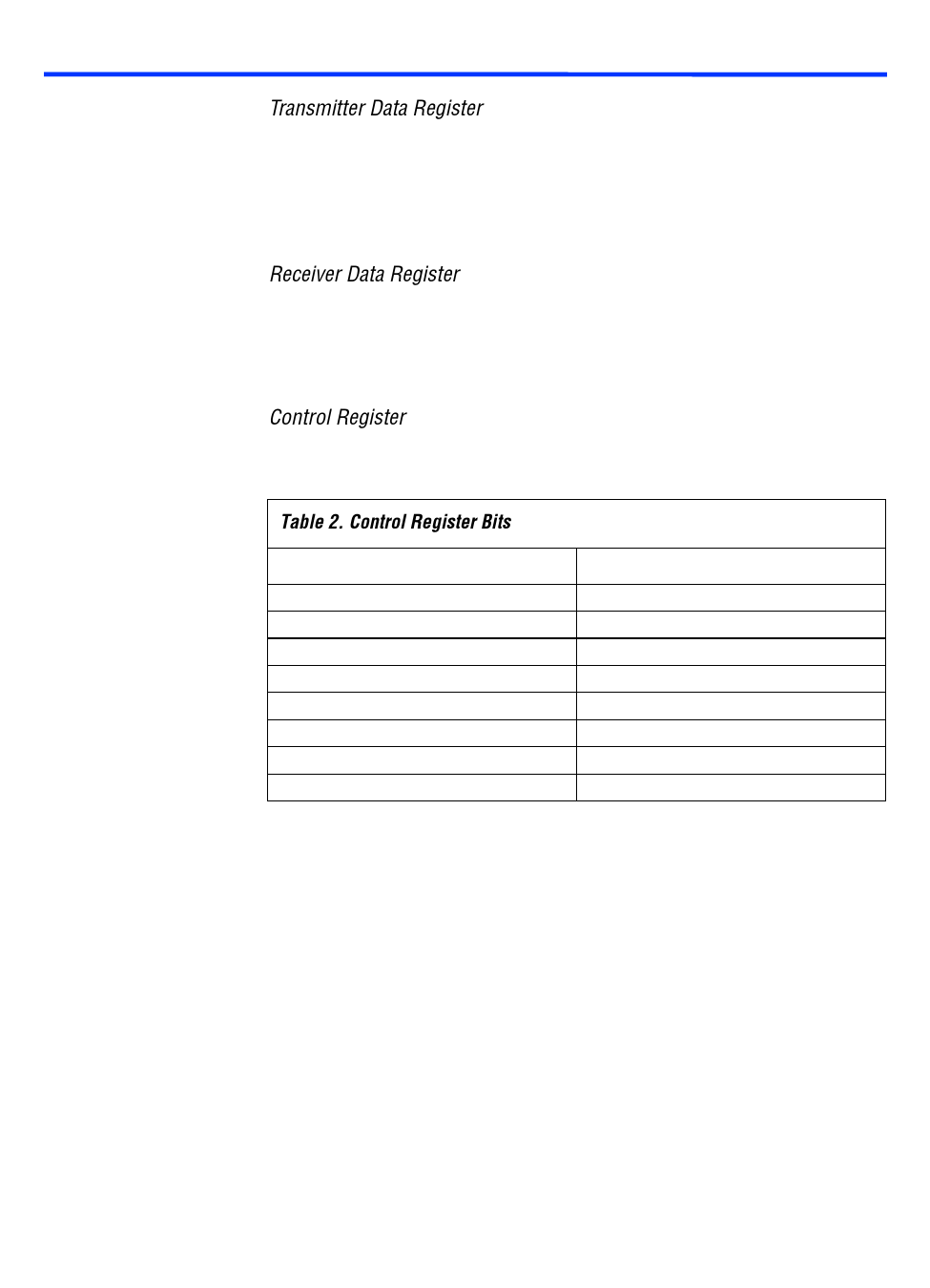

Control Register

The control register contains the control bits shown in Table 2.

Table 2. Control Register Bits

Data Bit

0

1

2

3

4

5

6

7

Signal Name

Counter divide select 0 (cds0)

Counter divide select 1 (cds1)

Word select 0 (ws0)

Word select 1 (ws1)

Word select 2 (ws2)

Transmitter control 0 (tc0)

Transmitter control 1 (tc1)

Receive interrupt enable (rie)

Counter Divide Select

Bits 0 and 1 of the control register are the cds bits, which determine the

ratio between the data rate and the clocks. The ratios when transmitting

and receiving are identical. The cds bits can also be used to reset the

a6850 to a known state. See Table 3.

84

Altera Corporation