LAN91C110 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LAN91C110 Datasheet PDF : 56 Pages

| |||

FEAST Fast Ethernet Controller for PCMCIA and Generic 16-Bit Applications

Datasheet

The receive byte count always appears as even; the ODDFRM bit of the receive status word indicates if the low byte of

the last word is relevant.

The transmit byte count least significant bit will be assumed 0 by the controller regardless of the value written in memory.

DATA AREA - The data area starts at offset 4 of the packet structure and can extend up to 2043 bytes.

The data area contains six bytes of DESTINATION ADDRESS followed by six bytes of SOURCE ADDRESS, followed by

a variable-length number of bytes. On transmit, all bytes are provided by the CPU, including the source address. The

LAN91C110 does not insert its own source address. On receive, all bytes are provided by the CSMA side.

The 802.3 Frame Length word (Frame Type in Ethernet) is not interpreted by the LAN91C110. It is treated transparently

as data both for transmit and receive operations.

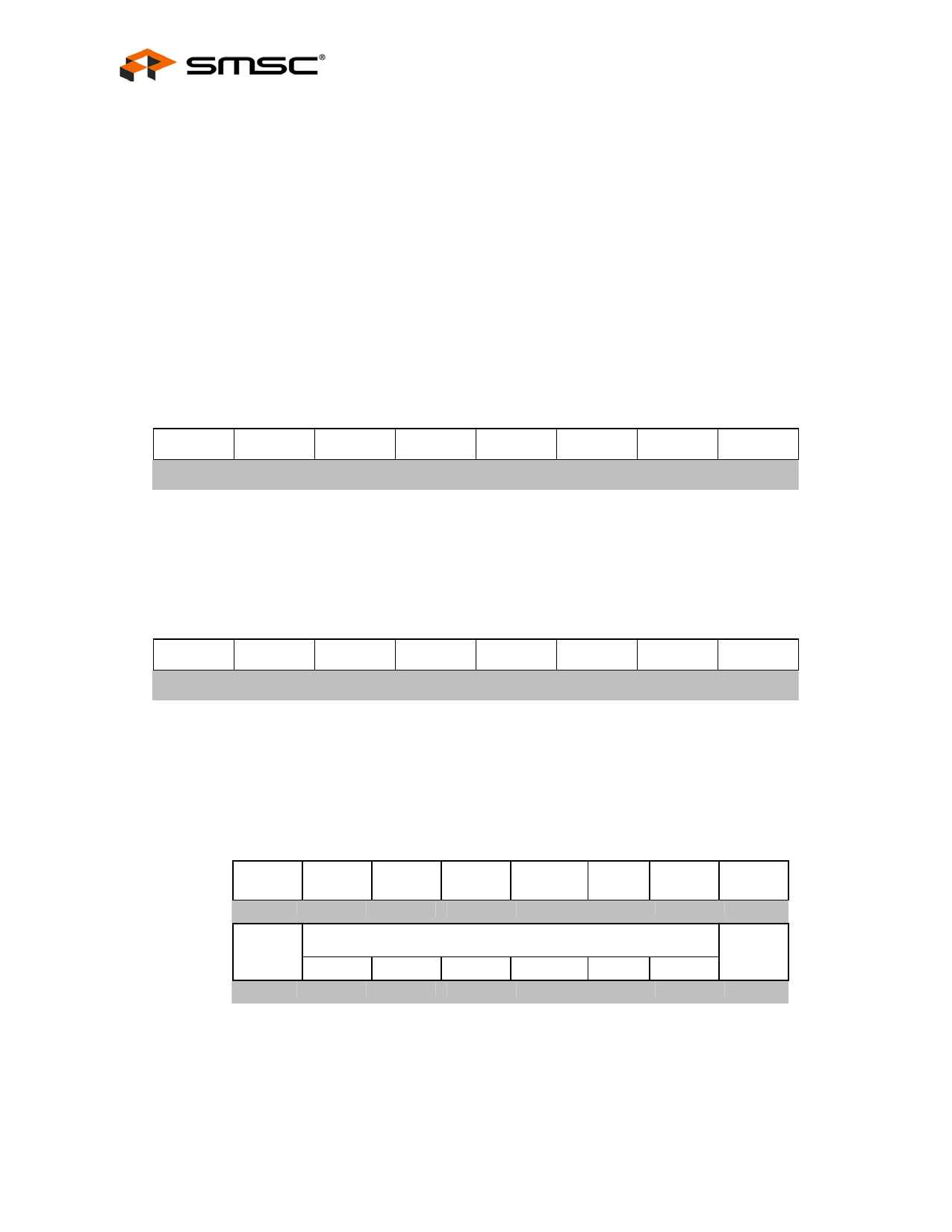

CONTROL BYTE - For transmit packets the CONTROL BYTE is written by the CPU as:

X

X

ODD

CRC

0

0

0

0

ODD - If set, indicates an odd number of bytes, with the last byte being right before the CONTROL BYTE. If clear, the

number of data bytes is even and the byte before the CONTROL BYTE is not transmitted.

CRC - When set, CRC will be appended to the frame. This bit has only meaning if the NOCRC bit in the TCR is set.

For receive packets the CONTROL BYTE is written by the controller as:

0

1

ODD

0

0

0

0

0

ODD - If set, indicates an odd number of bytes, with the last byte being right before the CONTROL BYTE. If clear, the

number of data bytes is even and the byte before the CONTROL BYTE should be ignored.

RECEIVE FRAME STATUS WORD

This word is written at the beginning of each receive frame in memory. It is not available as a register.

HIGH

BYTE

ALGN

ERR

BROD

CAST

BAD

CRC

ODD

FRM

TOOLNG

TOO

SHORT

LOW

BYTE

HASH VALUE

MULT

CAST

5

4

3

2

1

0

ALGNERR - Frame had alignment error. When MII SEL=1 alignment error is set when BADCRC=1 and an odd number of

nibbles was received between SFD and RX_DV going inactive.

SMSC LAN91C110 Rev. B

Page 16

DATASHEET

Revision 1.0 (11-04-08)