LAN91C110 Ver la hoja de datos (PDF) - SMSC -> Microchip

Número de pieza

componentes Descripción

Lista de partido

LAN91C110 Datasheet PDF : 56 Pages

| |||

FEAST Fast Ethernet Controller for PCMCIA and Generic 16-Bit Applications

Datasheet

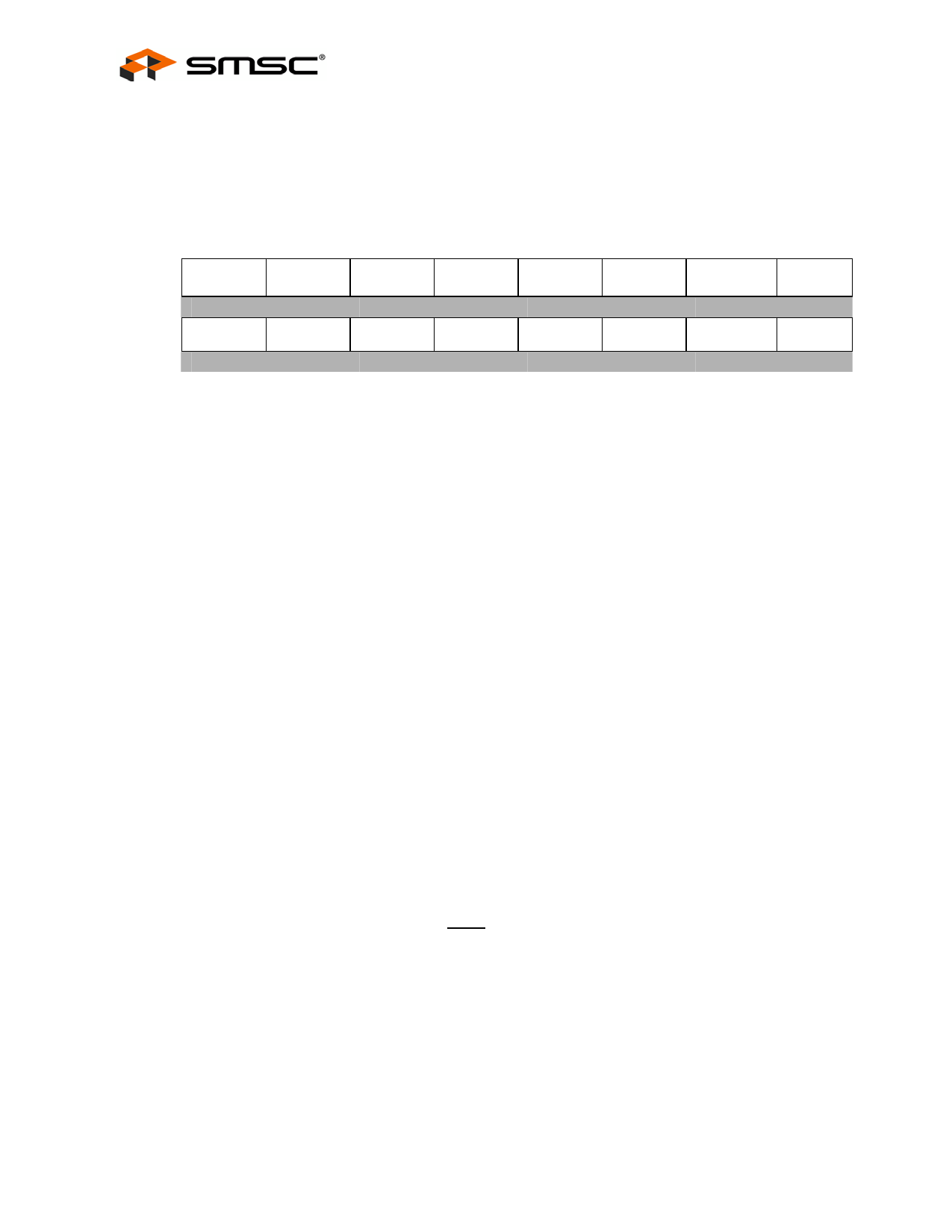

BANK 0

OFFSET

0

NAME

TRANSMIT CONTROL

REGISTER

TYPE

READ/WRITE

SYMBOL

TCR

This register holds bits programmed by the CPU to control some of the protocol transmit options.

HIGH

BYTE

LOW

BYTE

SWFDUP

0

PAD_EN

0

Reserved

0

Reserved

0

EPH

LOOP

0

Reserved

0

STP

SQET

0

Reserved

0

FDUPLX

0

Reserved

0

Reserved

0

FORCOL

0

Reserved

0

Reserved

0

NOCRC

0

TXENA

0

SWFDUP - Enables Switched Full Duplex mode. In this mode, transmit state machine is inhibited from recognizing carrier

sense, so deferrals will not occur. Also inhibits collision count, therefore, the collision related status bits in the EPHSR are

not valid (CTR_ROL, LATCOL, SQET, 16COL, MUL COL, and SNGL COL). Uses COL100 as flow control, limiting

backoff and jam to 1 clock each before inter-frame gap, then retry will occur after IFG. If COL100 is active during

preamble, full preamble will be output before jam. When SWFDUP is high, the values of FDUPLX and MON_CSN have

no effect. This bit should be low for non-MII operation.

EPH_LOOP - Internal loopback at the EPH block. Serial data is internally looped back when set. Defaults low. When

EPH_LOOP is high the following transmit outputs are forced inactive: TXD0-TXD3 = 0h, TXEN100 = TXEN = 0, TXD = 1.

The following and external inputs are blocked: CRS=CRS100=0, COL=COL100=0, RX_DV= RX_ER=0.

STP_SQET - Stop transmission on SQET error. If set, stops and disables transmitter on SQE test error. Does not stop on

SQET error and transmits next frame if clear. Defaults low.

FDUPLX - When set the LAN91C110 will cause frames to be received if they pass the address filter regardless of the

source for the frame. When clear the node will not receive a frame sourced by itself. This bit does not control the duplex

mode operation, the duplex mode operation is controlled by the SWFDUP bit.

NOCRC - Does not append CRC to transmitted frames when set. Allows software to insert the desired CRC. Defaults to

zero, namely CRC inserted.

PAD_EN - When set, the LAN91C110 will pad transmit frames shorter than 64 bytes with 00. For TX, CPU should write

the actual BYTE COUNT before padded by the LAN91C110 to the buffer RAM, excludes the padded 00. When this bit is

cleared, the LAN91C110 does not pad frames.

FORCOL - When set, the FORCOL bit will force a collision by not deferring deliberately. This bit is set and cleared only

by the CPU. When TXENA is enabled with no packets in the queue and while the FORCOL bit is set, the LAN91C110 will

transmit a preamble pattern the next time a carrier is seen on the line. If a packet is queued, a preamble and SFD will be

transmitted. This bit defaults low to normal operation. NOTE: The LATCOL bit in the EPHSR, setting up as a result of

FORCOL, will reset TXENA to 0. In order to force another collision, TXENA must be set to 1 again.

TXENA - Transmit enabled when set. Transmit is disabled if clear. When the bit is cleared the LAN91C110 will complete

the current transmission before stopping. When stopping due to an error, this bit is automatically cleared.

SMSC LAN91C110 Rev. B

Page 19

DATASHEET

Revision 1.0 (11-04-08)